به نظر میرسد انقلابی در صنعت نیمه هادی ها در راه است !!!!

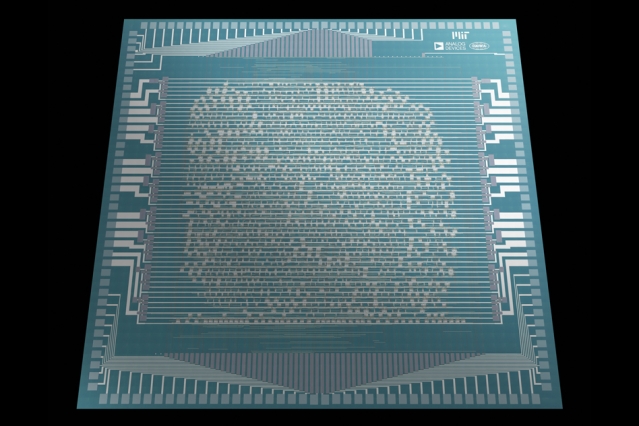

مهدنسان دانشگاه MIT و شرکت آنالوگ دیوایس (Analog Devices) یکی از پیچیده ترین تراشه های دنیا امروز فناوری و تکنولوژی را ساختند که در ترانزیستورهای های آن به جای سیلیکون از نانو لوله های کربنی استفاده شده .

این تراشه با تکنولوژی ساخته شده که به احتمال زیاد در آینده ایی نزدیک میتواند به صورت تجاری تولید شود . محققان ساختار معماری مجموعه دستورالعمل RISC-V را برای استفاده در تراشه انتخاب کردهاند و به نظر میرسد دلیل این است که RISC-V متن باز است و در نتیجه مشکلات مربوط به دریافت لایسنس و هزینههای مربوطه را ندارد. پردازنده ی RISC-V ساختار ۳۲ بیتی و آدرسدهی حافظهی ۱۶ بیتی دارد. چیپ نام برده شده قرار نیست در آینده ی نزدیک در مصارف عمومی به کار رود اما میتوان آن را کانسپتی در نظر گرفت که میتواند کدهای ساده برنامه نویسی را اجرا کند .

یکی از مزیت های ترانزیستور های ساخته شده با نانو لوله ی کربنی به جای سیلیکون این است که اجازه ی استفاده از ساختار چند لایه را میدهد , در نتیجه محصول نهایی می تواند یک تراشه سه بعدی بسیار فشرده باشد . مزیت دیگری که نانو لوله های کربنی دارند این است که می شود با هزینه بسیار کمتر ، تراشه های سه بعدی ساخته شود که عملکردی مشابه و یا بهتر از تراشه های سیلیکونی دارند .

طبق قانون مور که در سال ۱۹۶۵ بیان شد، تعداد ترانزیستورهای روی یک تراشه با مساحت ثابت، هر دو سال یکبار دوبرابر خواهد شد. اما بهمرور زمان، این قانون به حالت اشباع رسید و سرعت آن کمتر شد. در نتیجه با هر بهروزرسانی در تراشههای کامیپوتری که توسط شرکتهای تولیدکنندهی قطعات نیمههادی صورت گرفت و با هر بار فشردهترشدن فناوریهای ساخت، هزینهی مورد نیاز بیشتر و بیشتر شد. با افزایش هزینهی لازم برای تولید تراشههای سیلیکونی، ترانزیستورهای ساختهشده از نانولولههای کربنی با اینکه در حال حاضر از دنیای واقعی فاصله دارند، به مرور بیشتر مورد اقبال قرار خواهند گرفت.

ماکس شولاکر (Max Shulaker) ، استاد یار دانشگاهMIT ، کار و تحقیق روی این پروژه را از 10 سال پیش شروع کرد. در سال 2013 ، گروه تحقیقاتی تحت نظر او توانستند یک پردازندهی یک بیتی با ۱۷۸ ترانزیستور بسازند. اما حالا ، تیم او قادر به ساختن پردازنده مبتنی با معماری RISC-V وبا 15,000 ترازیستور با پشتیبانی از ساختار ۳۲ بیتی و آدرسدهی حافظهی ۱۶ بیتی هستن .

شولاکر به مجلهی IEEE Spectrum گفت:

۱۰ سال پیش امیدوار بودیم که این کار امکانپذیر باشد. حالا میدانیم که امکانپذیر است و میدانیم که میتوان این کار را در مقیاس تجاری هم انجام داد.

چطور RV16X-NANO ساخته شد؟

مهندسان MIT، Analog Devices و شرکت Skywater Technology، تراشهی نانولولهی کربنی RISC-V را با نام RV16X-NANO و با همکاری یکدیگر ساختند. آنها برای مشکلاتی که بر سر راه ساخت چنینی تراشهای بود، راهحلهای خلاقانهای یافتند. اولین مشکل، رسیدن به ساختارهای کربنی خالص و بینقص بود. دومین مشکل این بود که آنها نمیتوانستند ترانزیستورهای مکمل نوع n و نوع p را به گونهای بسازند که بتواند یک مدار منطقی مکمل (Complementary Logic Circuit) را تشکیل دهد.

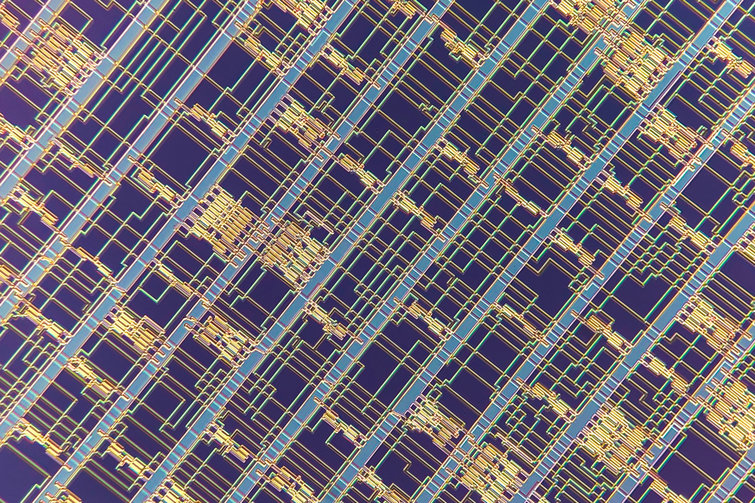

یکی از راههای ساخت ترانزیستورهایی از جنس نانولولهی کربنی این است که آنها را روی یک ویفر سیلیکون پخش کنند. برای این کار یک ویفر سیلیکونی با ابعاد ۱۵۰ میلیمتر را در یک محلول نانولولهی کربنی غوطهور میکنند. با این کار نانولولههای کربنی در مسیر مدارها و دروازههای منطقی که روی ویفر حکاکی شدهاند، رسوب میکنند. در عین حال نانولولههای کربنی در دستههای ۱۰۰۰ تایی یا بیشتر در کنار یکدیگر قرار میگیرند و این دستهها بهعنوان ترانزیستور قابل استفاده نیستند. اگر قرار باشد ترانزیستورهای نانولولهی کربنی در مقیاس بزرگ ساخته شود، مشکل تجمع نانولولههای کربنی بسیار قابلتوجه خواهد بود چون در این صورت تعداد بسیار زیادی از تراشهها باید دور ریخته شوند.

کریستین لائو، یکی از دانشجویان شولاکر، توانست راهحلی برای این مشکل پیدا کند. این راهحل که RINSE یا Removal of Incubated Nanotubes through Selective Exfoliation نامیده میشود، به سازندهی ترانزیستور امکان میدهد که دستههای اضافی نانو لولهی کربنی را از روی ویفر پاک کند و تنها ترانزیستورهای یکنواخت و سالم را روی آن نگه دارد. برای این منظور، محصول اولیه با یک لایهی پلیمری پوششدهی میشود و سپس در یک حلال قرار میگیرد. این کار باعث میشود تا دستههای تجمعی اضافی نانولولهی کربنی حذف شوند.

یکی دیگر از مشکلات ساخت این ترانزیستورها، خلوص نانولولههای کربنی است. مشکل از آنجا ناشی میشود که درصد بسیار اندکی از نانولولههای کربنی دارای رسانایی فلزی بالایی هستند که باعث میشود یک ترانزیستور، همواره خاموش یا همواره روشن باشد. این اتفاق ممکن است به نابودی پردازنده منجر شود. در حال حاضر بهترین روشهای ساخت نانولولهی کربنی میتوانند محصولی با خلوص ۹۹٫۹۹ درصد تولید کنند؛ بدین معنا که ۹۹٫۹۹ درصد نانولولههای حاصل نیمههادی و ۰٫۰۱ درصد آنها فلزی هستند. این میزان خلوص برای ساخت تراشههای پیچیدهای که با نانولولههای کربنی ساخته میشوند، بسیار پایین است چون به لحاظ تئوری میزان خلوص لازم برای جلوگیری از ایجاد مشکل در عملکرد ترانزیستورها ۹۹٫۹۹۹۹۹۹ درصد است. یکی از پژوهشگران پسادکتری در تیم شولاکر به نام گیج هیل (Gage Hill) توانست راهحلی برای این مشکل پیدا کند و آن را (DREAM (Designing Resiliency Against Metallic نامید. بهگفتهی او بزرگترین مشکل ناشی از خلوص پایین نه افزایش توان مصرفی تراشههای حاصل، بلکه ایجاد نویز بود. راهحل آنها برای این مشکل، ترکیب گیتهای منطقی به گونهای بود که بتواند نویز را کاهش دهد.

در واقع، نکتهی مهم در این میان، نحوهی بهکارگیری گیتهای منطقی است. آنچه محققان مشاهده کردهاند، این است که یک نانولولهی کربنی فلزی میتواند گیت را نابود کند، اما همین نانولهی فلزی اگر به شیوهی خاصی در گیت منطقی دیگری بهکار رود، مشکلی ایجاد نمیکند. بنابراین آنها نرمافزاری را طراحی کردند که پیشبینی کند یک نانولهی کربنی ناخالص در چه شرایطی کمترین آسیب را ایجاد میکند، سپس تراشهی مورد نظر را با چنین معماری پیشنهادی تهیه کردند. ماکس شولاکر در این مورد گفته است:

این راهحل به ما کمک میکند تا بتوانیم نانولولههای کربنی موجود در بازار با خلوص ۹۹٫۹۹ درصد را خریداری کنیم، سپس آنها را روی یک ویفر پخش کنیم و بعد مدار موردنظرمان را به شیوهی معمول بسازیم، بدون اینکه لازم باشد عملیات خاصی انجام دهیم.

سومین راهحل در این راستا (MIXED (Metal Interface Engineering crossed with Electrostatic Doping نام دارد و به مهندسان کمک میکند تا بتوانند ترانزیستورهای نوع n (نیمههادی اکسید فلزی نوع n مبتنی بر انتقال الکترونی) و نوع P (نیمههادی اکسید فلزی نوع p مبتنی بر انتقال حفرهای) را بسازند. این دو نوع ترانزیستور سالها است در تراشههای سیلیکونی استفاده میشوند. در مورد این پردازندهها مسئلهی اصلی جداسازی ترانزیستورهای نوع p و n است؛ چون باید برای بیت «۱» روشن و برای بیت «صفر» خاموش باشند و برعکس. این ویژگی در سیستمهای باینری بسیار حائز اهمیت است. اولین تراشهی شولاکر که یک بیتی بود، تنها ترانزیستور نوع p داشت.

روند ساخت ترانزیستورهای n و p از جنس نانولولههای کربنی که با نام MIXED معرفی شده، یک فرایند دما پایین است و در نتیجه میتوان چند لایه ترانزیستور را با این روش روی لایههای دیگر ایجاد کرد، بدون اینکه نگرانی در مورد آسیبدیدن این لایهها وجود داشته باشد. در این روش که ترکیبی از اضافهکردن فلز و ناخالصسازی الکترواستاتیک است، پس از حذف دستههای اضافی نانولولهی کربنی از روی ویفر، مقادیر اندک پلاتینیوم یا تیتانیوم به هر ترانزیستور اضافه میشود و سپس ویفر با یک اکسید پوشانده میشود. این اکسید، نقش مهر و موم را خواهد داشت و عملکرد پردازنده را بهبود میبخشد.

شولاکر و تیم او در مقالهای که در مورد این تراشه منتشر کردهاند، علاوه بر مزایا، در مورد محدودیتهای آن هم مطالبی را بیان کردهاند. از مواردی که در این مورد بیان شده، سرعت کلاک تراشه است که در حال حاضر بالغ بر ۱۰ کیلوهرتز بوده و باید بهبود یابد. پردازندههای نانولولهی کربنی هنوز در فاز آزمایشگاهی قرار دارند اما آنچه مشخص است، ساخت آنها در این مرحله نشان میدهد که چگونه میتوانیم آنها را بهصورت بهینه بسازیم. احتمالاً اولین بازار هدف این تراشهها، پردازندههای سروری نیستند اما ممکن است در دستگاههایی مانند میکروکنترلرها که نیاز به عملکرد سطح بالا ندارند، استفاده شوند. استفاده از RISC-V ISA در این دستگاهها انتخاب هوشمندانهای است.

منبع : https://www.tomshardware.com